Converged, Efficient and Safe Architecture based on Near Memory Accelerators

— Preview

Rethink hardware so that it is co-designed with the application, with a view to converged architecture and trust in an environment with abundant data to process

Denis Dutoit, Head of the computing and digital architectures program at CEA-List

Keywords: Digital architecture, rack-scale computing, disaggregated heterogeneous architectures, memory-centric architectures, hardware gas pedals, energy efficiency, design, formal methods

European cloud sovereignty includes control over processors and gas pedals. With Dennard’s Law coming to an end and Moore’s Law slowing down, processor performance will evolve towards more parallelism (multi-core), more specialization (gas pedals), and integrating new interconnections. Virtualization, by separating hardware resources from logical ones, facilitates converged architectures, making the cloud more modular, fast and agile. However, this increased complexity makes the intermediate adaptation layer harder to validate and more prone to failure.

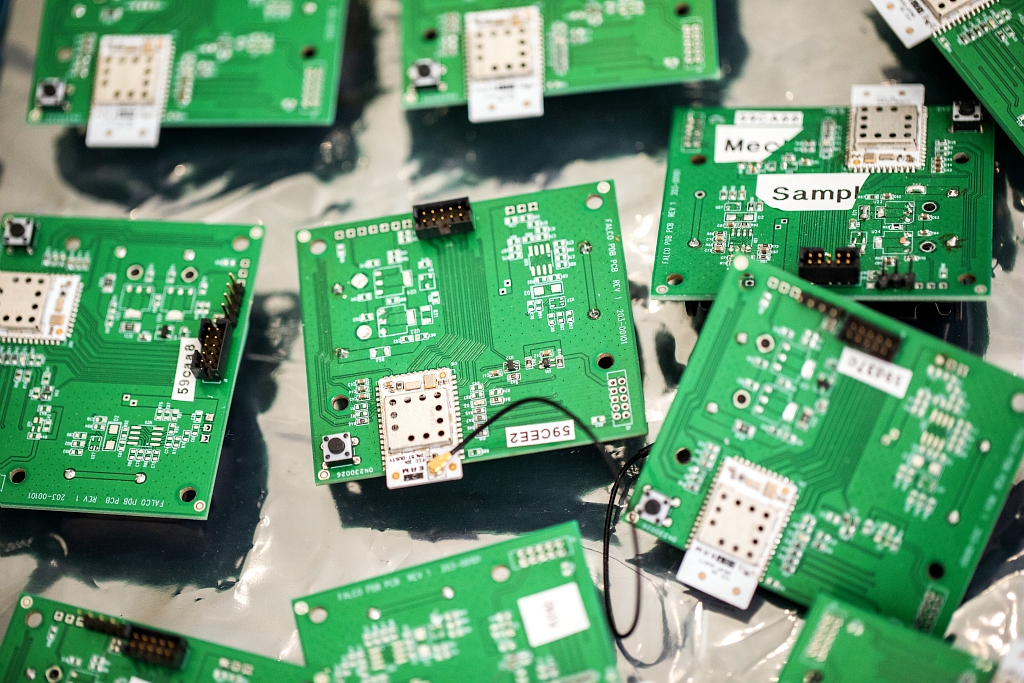

The Archi-CESAM project proposes to rethink hardware (computation, memory and interconnection) so that it is co-designed with the application in a converged and trusted architecture perspective, in an environment known for its abundance of data to be processed. The Archi-CESAM project tackles this major Cloud evolution with a global, coordinated approach to distributed architectures, acceleration, interconnection and security bricks, not forgetting design methods.

— Missions

— Our researches

— Partners

Consortium

Inria, CEA, Université de Rennes, Télécom SudParis, GINP, CNRS

Our teams in France

— Publications

Conference papers

- Philippe Ledent, Radu Mateescu, Wendelin Serwe. Improving PSS Test Generation Using Model Checking and Conformance Testing. FDL 2024 - 27th Forum on specification and Design Languages, Sep 2024, Stockholm, Sweden. pp.1-9, ⟨10.1109/FDL63219.2024.10673842⟩. ⟨hal-04719995⟩

- Rémi Dulong, Nathan Felber, Pascal Felber, Gilles Hopin, Baptiste Lepers, et al.. P 4 ce: consensus over RDMA at line speed. ICDCS 2024 - IEEE 44th International Conference on Distributed Computing Systems, Jul 2024, Jersey City, United States. pp.508-519, ⟨10.1109/ICDCS60910.2024.00054⟩. ⟨hal-04895326⟩

Other projects